自動車用メモリ保護ユニットに隠れた脆弱性を解明

はじめに

コンピュータの画面でこの文章を読んでいる今、このやりとりを可能にしているデバイスには間違いなくメモリ管理ユニット(MMU)が搭載されています。普段はあまり意識されないものの、MMUは現代のコンピューティングにおいて欠かせない存在であり、日々私たちが使用しているソフトウェアをスムーズに動作させるために、背後でメモリリソースを管理しています。スマートフォンからインターネットを支える強力なサーバーに至るまで、MMUはメモリの割り当てを調整し、パフォーマンスを最適化し、セキュリティ脅威から保護する中心的な役割を担っています。ここまで説明しましたが、今回のブログ記事ではMMUについて取り上げるわけではありません。なぜなら、自動車の電子制御ユニット(ECU)の大部分を支えるマイクロコントローラユニット(MCU)には、通常MMUが実装されていないためです。

代わりに今回のブログでは、MMUの「弟分」とも言えるメモリ保護ユニット(MPU)についてご紹介します。MMUは、中央処理装置(CPU)のメモリ管理において中心的な役割を果たすため注目を集めがちですが、MPUはメモリ保護を強化し、不正アクセスを防ぎ、セキュリティ脅威から保護するという重要な役割を果たしています。それにもかかわらず、MPUは目立たない存在になりがちです。

今回のブログでは以下の内容について説明します。

- 現代のMPUの機能:

最新のメモリ保護ユニット(MPU)の機能と、自動車分野におけるセキュリティ確保における特別な役割について解説します。 - 現代のMCUで使用されるMPUの種類:

最新のマイクロコントローラユニット(MCU)で使用されるさまざまなMPUの種類について議論します。 - 発見された脆弱性:

発見された脆弱性(CVE-2023-48010およびCVE-2024-33882)の詳細について説明します。 - 責任ある開示プロセス:

チップベンダーとの責任ある脆弱性開示プロセスの概要を紹介します。 - 推奨される緩和策:

発見された脆弱性に対処するための緩和策を提案します。

背景

MMUからMPUへ

現代の中央処理装置(CPU)では、MMUは通常、仮想アドレス空間を管理するハードウェアデバイスとして使用され、仮想アドレスを物理アドレスにマッピングします。さらに、MMUはメモリに関連するタスクも実行します。MMUのメモリ保護機能は、プログラムが事前に要求していないメモリにアクセスしようとする試みをブロックするよう設計されており、これにより、誤動作するプログラムがメモリを使い果たしたり、悪意のあるコードが他のプログラムのデータを読み書きすることを防ぎます。

初期のマイクロプロセッサ設計では、1965年のIBM System 360や1986年のApple Macintoshなど、仮想メモリマッピングやメモリアクセス権限を処理するためにMMUが含まれていました。

一方、小型のマイクロコントローラは、MMUによる仮想メモリマッピングの負担を必要としませんでした。しかし、マイクロコントローラのアーキテクチャにおける弱点には、オペレーティングシステム、ユーザーソフトウェア、変数が共通のメモリを使用していたことがあげられます。この問題は、市場に複数コアのマイクロコントローラが登場し始め、異なるセキュリティおよび安全レベルの複数のアプリケーションが同じ共通メモリを使用するようになるとさらに複雑になりました。

より高いレベルのセキュリティを必要とするアプリケーション、例えば自動車産業では、メモリアクセス権限のみを管理するMMUの縮小版を実装しました。これがメモリ保護ユニット(MPU)の始まりです。

MPU:現代のサイバーセンティネル(見張り番)

メモリ保護ユニット(MPU)は、メモリの「門番」として機能するプログラム可能なハードウェアユニットです。これにより、メモリを異なる領域に分割し、それぞれの領域に対してメモリアクセス権限(特権アクセスのみや完全アクセスなど)やメモリ属性(読み取り/書き込み/実行など)を設定することが可能になります。

非常に基本的な説明をすると、MPUはメモリリソースへのアクセス制御を監視します。「アクセス制御」とは、「コンピューティング環境において、誰が、または何が、リソースを閲覧または使用できるかを規制するセキュリティ技術」1 と定義されます。これはセキュリティの基本的な概念であり、組織にとってのリスクを最小限に抑えるものです。

より広い意味では、『Computer Security: Principles and Practice』において次のように述べられています。

「…すべてのコンピュータセキュリティはアクセス制御に関するものである。アクセス制御は、特定のシステムリソースに誰がまたは何がアクセスできるか、また各事例で許可されるアクセスの種類を指定するセキュリティポリシーを実施するものである。」2

この意味では、MPUは一般的なセキュリティ、特に組み込みシステム(自動車を含む)のセキュリティにおける主要な防御策の1つです。ある研究『From MMU to MPU: adaptation of the Pip kernel to constrained devices(MMUからMPUへ:拘束デバイスへのPipカーネルの適応)』3 では、マイクロコントローラでMPUを有効化すると、性能とエネルギー消費の両面で16%のオーバーヘッドが発生するものの、アクセス可能なアプリケーションメモリのアタックサーフェスが100%からわずか2%!に削減できることが示されています4。

許可されていないメモリへのアクセスを試みると、ハードウェアフォルトが発生し、潜在的な攻撃を実質的に停止し、不正なアクセスを、例えば、システムをリセットして攻撃者を「振り払う」ような形で対応します。

MPUを有効化すると、ランダムアクセスメモリ(RAM)上での実行アクセスを制限することが可能です。そのため、たとえ攻撃の第一段階として、ターゲットのECUスタックメモリにスタックバッファオーバーフローの脆弱性を利用して悪意あるコードを書き込むことに成功しても、MPUの保護によりそのコードをスタックメモリ領域で実行することはできなくなります。

自動車の保護ユニット

メモリ保護ユニット(MPU)は、自動車業界において、車両内の組み込みシステムのセキュリティ、信頼性、安全性を向上させる重要な役割を果たしています。以下にその役割の概要を示します。

- セキュリティ強化

MPUはメモリ保護メカニズムを実装・適用することで、自動車システムのセキュリティを向上させます。これにより、不正アクセスやデータの破損、意図しないコードの実行を防ぎ、外部からの脅威から重要な情報や機能を保護します。 - アクセス制御の厳格な適用

MPUは異なる特権レベルを区別し、事前に設定されたアクセス制御ポリシーを厳格に適用ができます。

自動車アプリケーションでは、ハードウェアセキュリティモジュール(HSM)、ブートローダーアプリケーション、セキュアブートプロセス、サードパーティアプリケーションなど、異なる特権レベルを持つコンポーネントが頻繁に使用されます。例えば、HSMメモリへの不正なアプリケーションからのアクセスをブロックする機能は、自動車システム設計者にとって重要なセキュリティツールです。 - 安全性の向上

MPUはメモリ保護ポリシーを適用し、重要なソフトウェアコンポーネントを分離することで、安全性が求められるシステムの構築を支援します。これにより、エラーや悪意のある干渉が車両の安全を損なうリスクを低減します。 - アプリケーションの分離

MPUは、車両内の組み込みシステムにおける異なるアプリケーションの分離を可能にします。それぞれのアプリケーションやソフトウェアモジュールに専用の保護されたメモリ領域を割り当てることで、アプリケーション間での干渉やデータ破損を防ぎます。この分離は、重要な機能の完全性を維持し、1つのアプリケーションへの攻撃が同一システム内の他のアプリケーションに影響を与えないようにするために不可欠です。 - MPUは、コア、DMA(Direct Memory Access)コントローラ、CAN、USB、GPUなどのコア-外部のペリフェラルコントローラなど、システム内のバス・マスタの相互作用を管理し、安全を確保する上で極めて重要な役割を果たします。バス・マスタにおいてMPUは、データ転送の完全性とセキュリティを保証する重要なコンポーネントとして機能します。メモリ保護メカニズムを提供することで、MPUは異なるバス・マスタの分離を可能にし、共有メモリへのアクセスにおける意図しない干渉や潜在的な競合を防ぎます。この機能は、さまざまなコアがメモリ資源に同時にアクセスする可能性のあるマルチコアシステムにおいて特に重要です。MPUは、安全かつ明確に定義された境界の確立に貢献し、各バス・マスタが割り当てられたメモリ空間内で動作することを可能にします。MPUは、不正または悪意のある行為から保護するためにアクセス制御を実施し、高速なコア外転送中のデータの機密性と完全性を保証します。

MPUの種類

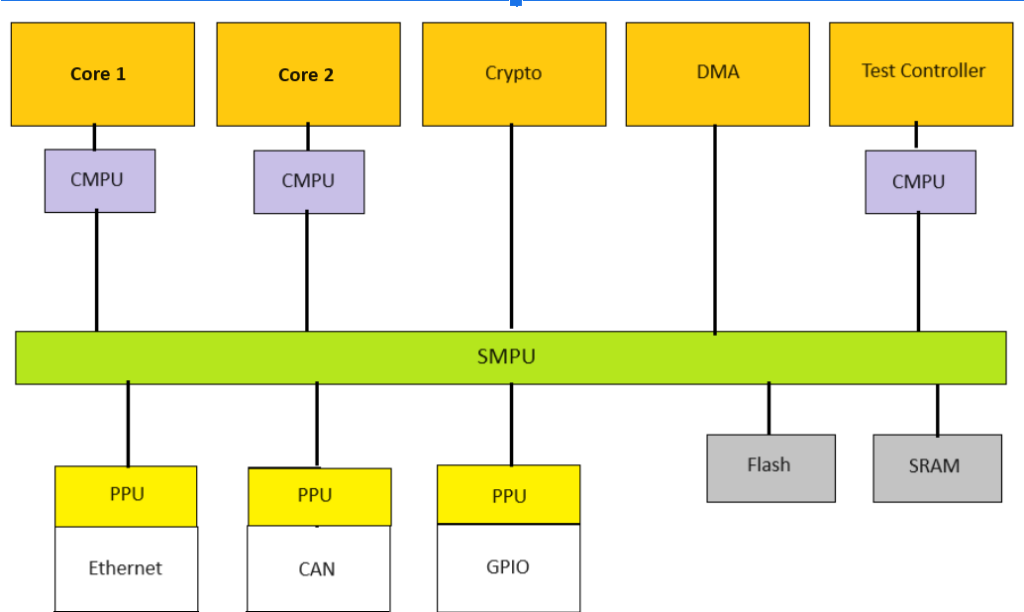

すべてのメモリ保護ユニット(MPU)が同じ設計で作られているわけではなく、アーキテクチャによってさまざまな種類が存在します。しかし、以下の例のブロック図に示されるように、一般的に次の3つの主要なタイプに分類することができます。

コアMPU(CMPU)

CMPU(Core MPUまたはCPU MPUとも呼ばれる)は、マイクロコントローラの各コアに直接統合されたメモリ保護ユニットです。コアレベルで動作し、細かいメモリ保護およびアクセス制御メカニズムを提供します。CMPUは、コア自身が実行するコードおよびデータアクセスに対して、メモリ保護ポリシーを適用することを可能にします。通常、複数のメモリ領域ごとにアクセス権限(読み取り、書き込み、実行)や特権レベルを設定することができます。CMPUは、マイクロコントローラの各コアで実行される個々のソフトウェアプロセスのメモリアクセスを保護するために不可欠な役割を果たします。

システムMPU(SMPU)

SMPU(System MPUとも呼ばれる)は、システム全体のメモリ空間を保護するために設計されたメモリ保護ユニットです。コアの視点で保護を提供するCMPUとは異なり、SMPUはシステムレベルで動作し、システム内のバストランザクション5を対象としたメモリ保護を提供します。CMPUがコアで実行されるソフトウェアコードから発生するバストランザクションを監視・制御するのに対し、SMPUはダイレクトメモリアクセス(DMA)やHSMなどのハードウェア関連のメカニズムを含むシステム全体のバストランザクションを制御します。SMPUのアドレス領域は通常、バストランザクションの発信元によって定義されます。例えば、SMPUはHSMに共有メモリ内の特定のアドレス範囲へのアクセスを許可するように設定される一方、他の発信元からのすべてのバストランザクションをブロックするように構成することができます。

周辺機能保護ユニット(PPU)

PPU(Peripheral MPUとも呼ばれる)は、組み込みシステム内のメモリマップドレジスタを保護するために特化されたメモリ保護ユニットです。PPUは、通信インターフェース、タイマー、I/Oポートなどの周辺機器に特化したアクセス制御およびセキュリティ機能を提供します。これにより、プロセッサコアや外部バスマスターによって開始される周辺機器へのアクセスに対し、アクセス権限や制限を適用することが可能です。PPUは重要なシステム周辺機器への不正または悪意のあるアクセスを防ぎ、周辺機器とのやり取りのセキュリティと信頼性を向上させます。

CVE-2023-48010とCVE-2024-33882

注意深く設定されたメモリー保護ユニットは、攻撃者にとって強力な対抗手段となります。しかし、「鎖はその最も弱い部分と同じ強さしかない」という決まり文句があります。もし攻撃者が完璧に設定されたMPUを無効化することができれば、当然ながらMPUの保護機能が失われてしまいます。

これら2つの脆弱性、CVE-2023-48010とCVE-2024-33882は、いずれもPowerPCマイクロコントローラの特定の設計に関連する、我々が発見したハードウェア脆弱性です。これらの脆弱性は、特権を持つ攻撃者がSMPU(システム・メモリ保護ユニット)全体を停止させることを可能にし、その結果、保護されたメモリ領域への読み書きを可能にします。PowerPCマイクロコントローラのデータシートによれば、あるハードウェア機能により、攻撃者がSMPUを無効化しようとしても、初期設定後もSMPUが有効な状態に保たれるはずですが、実際にはこの機能はシリコンに実装されておらず、SMPUはこのような攻撃に対して脆弱なままであることが明らかになっています。

その結果、ソフトウェアの設計者は、データシートに詳述されている対策を講じることで、保護されているかのような印象を抱いたまま、実際には保護されておらず、システムにリスクがあることにまったく気づかない可能性があります。

背景:PowerPCアーキテクチャ

最初のPowerPCマイクロコントローラは、1990年代半ばにモトローラ(後のFreescale Semiconductor)によって製造されました。これらのマイクロコントローラはMPC5xxシリーズとして知られ、PowerPCアーキテクチャが、自動車アプリケーションを含む組み込みシステム市場に進出した最初の例となりました。MPC5xxファミリーの起源は、1990年代初頭にIBM、Apple、モトローラが共同で進めた取り組みにまでさかのぼります。

RISCベースの設計により、高い性能と効率を兼ね備えたPowerPCプロセッサは、1990年代後半には自動車システムに採用されるようになりました。当初はエンジン制御やトランスミッション制御といったタスクに使用されていましたが、リアルタイム処理能力と過酷な環境下での耐久性により、インフォテインメントシステムや先進運転支援システム(ADAS)など、幅広い用途にとって欠かせない存在となりました。

2000年代半ばには、STMicroelectronicsとFreescale Semiconductor(現在のNXP Semiconductors)が共同開発したPowerPCアーキテクチャに基づくMPC56xx/SPC56xファミリーが登場しました。これらは特に自動車アプリケーション6

向けに設計されており、両メーカー間でピン互換性があり、マイクロコントローラはほぼ同一の仕様を持っています。

脆弱性

(1) CVE-2023-48010

PlaxidityX(旧アルガス)では、ペネトレーションテストやセキュリティ研究に加えて、自動車システム向けのセキュリティ製品およびソリューションの設計と開発も行っています。今回のケースでは、将来の製品に向けた概念実証(PoC)を開発しました。どのシステムを採用するかを決定する前に行う評価の一環として、このPoCはSTMicroelectronicsのPowerPC SPC58Nファミリーのマイクロプロセッサを基に構築しました。上述の通り、これらのマイクロコントローラは特に自動車用途向けに設計され、広く使用されているためです。

SPC58Nは、自動車のASIL-D7, 規格やセキュリティアプリケーション向けに設計された、トリプルコアの32ビット「Powerアーキテクチャ」8 マイクロコントローラです。

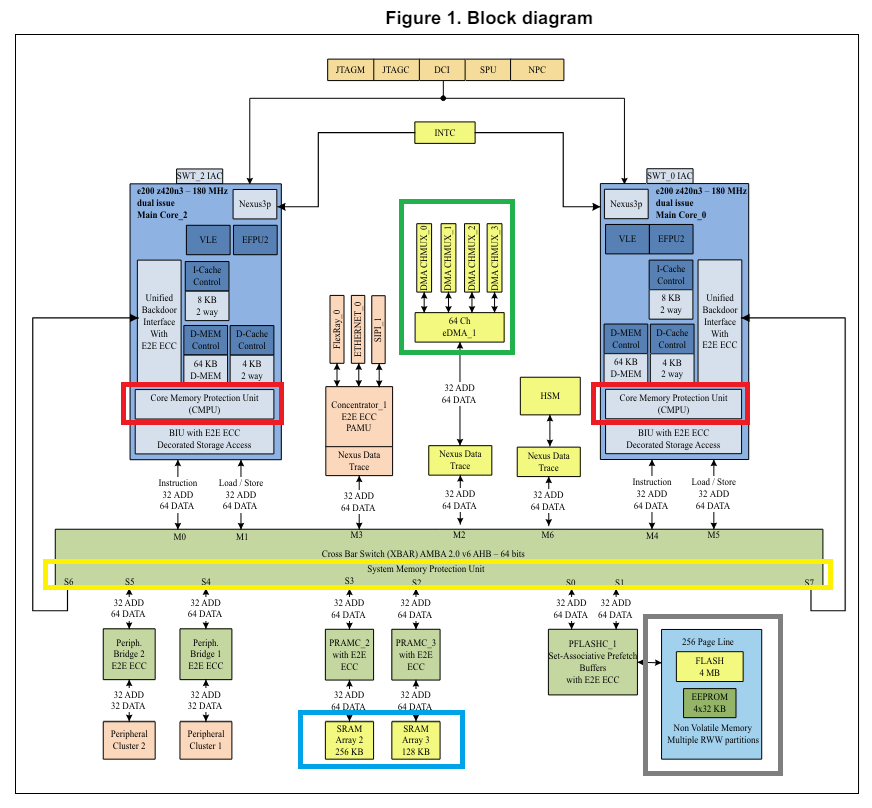

以下は、このチップのデータシートから引用したブロック図です。

図の下部には、チップのメモリがあります。フラッシュメモリとEEPROMはグレーで、スタティックRAMは青で示されています。これらのメモリは定義上、すべてのコアおよび周辺機器から共通してアクセス可能です。

図の上部には各コアが配置されており、それぞれに独自のコアメモリ保護ユニット(CMPU – 赤い長方形で示されています)と、コア間に配置された64のDMAチャネル(緑で示されています)があります。

コア、DMAチャネル、およびメモリの間には、黄色の長方形で示されたシステムメモリ保護ユニット(SMPU)が配置されています。

各コアで多様なアプリケーションが動作し、それぞれが異なる安全性およびセキュリティレベルを持つことが事前に分かっていたため、私たちはCMPUとSMPUの設定を慎重に定義することに取り組みました。

CMPUと制限

各コアメモリ保護ユニット(CMPU)は、各コアから発生するすべての命令フェッチとデータメモリアクセスを監視します。CMPUは、システムソフトウェアがメモリ領域とその関連するアクセス権限を定義するために使用するハードウェア機能です。CMPUは、ソフトウェアが権限を違反してメモリ領域にアクセスしようとすると例外を発生させ、システム設計者が介入して適切に例外を処理できるようにします。

セキュリティの観点から、CMPUは以下の2つの主な理由により、全体的なセキュリティ体制の非常に重要な部分となっています。

- CMPUは、スタックバッファオーバーフローを検出できるマイクロプロセッサアーキテクチャ内で唯一のエンティティです。スタックバッファオーバーフローは、プログラムがスタック上のバッファに収まる以上のデータを書き込むことで発生し、隣接するメモリアドレスをオーバーフローさせます。この問題は、入力データが適切に検証または制限されていない場合に発生し、攻撃者が関数の戻りアドレスやスタック上の他の重要なデータを上書きできるようになります。その結果、攻撃者がスタック上で悪意のあるコードを実行し、プログラムの正常な動作を妨害することで、任意のコードを実行する可能性が生じます。

マイクロコントローラ上で動作するすべてのアプリケーションのスタック領域を慎重に定義することで、設計者はCMPUを構成し、そのスタック領域での実行をブロックするように設定できます。これにより、攻撃対象領域を大幅に制限できます。 - CMPUは、アプリケーションの読み取り/書き込み操作を効果的に制限します。これにより、攻撃者が任意のコア上でコードの実行を得た場合(例えば、悪意のあるサードパーティコードを実行することで)、適切に構成されたCMPUが悪意のあるメモリアクセスを検出し、攻撃者の行動を妨害することを保証します。

しかし、本当にそうでしょうか?

上記のブロック図を振り返ると、各コアに適切に構成されたCMPUがあることで、コア自身からのメモリアクセスを防ぐのには役立つものの、Direct Memory Access(DMA)、Ethernet、HSMなどの特別な周辺機器を悪用して攻撃者がメモリにアクセスすることを防ぐことはできません。

このような攻撃を効果的に防御するために、SMPU(システムメモリ保護ユニット)が必要となります。

システムMPU(SMPU)

一見すると、SMPUはCMPUと非常に似ています。SMPUもシステムソフトウェアがメモリ領域とその関連するアクセス権限を定義するために使用するハードウェア機能であり、権限違反が発生した場合には、システム設計者が介入して例外を処理できるようにします。

しかし、SMPUにはCMPUにはない特別な機能があります。それは、SMPUが各バスマスターごとのメモリアクセスを同時に監視および評価することです。

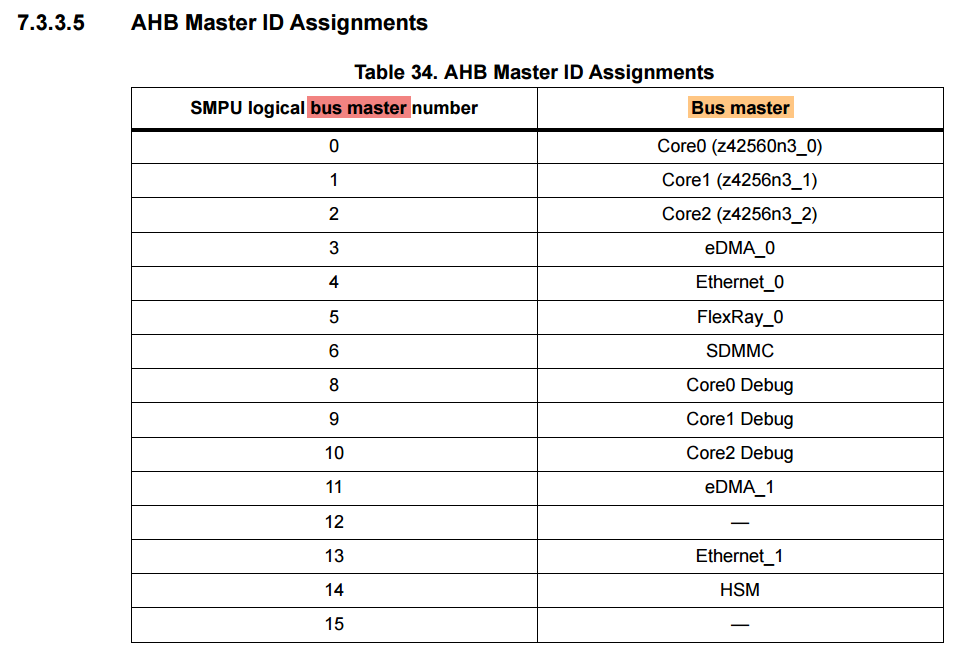

以下は、SPC58Nで利用可能なバスマスターの一覧です。

各バスマスターには、それぞれ指定されたメモリ領域へのアクセスを管理するための読み取り/書き込み/アクセス禁止のフラグが設定されています。たとえば、SMPUを特定のメモリ領域をHSMのみがアクセス可能とし、他のすべてのマスターを拒否するように設定することができます。この場合、CMPUがHSMの特定アドレスへのアクセスをブロックしないとしても、HSMメモリを読み書きしようとする試みはすべてSMPUによって効果的にブロックされます。

もう一つの例はDMAによるアクセスです。Core1上で動作するアプリケーションがCore1のCMPUによって特定のメモリ領域へのアクセスをブロックされている場合でも、攻撃者がDMAハードウェアを利用してその禁止されたメモリ領域に読み取り/書き込みアクセスを取得し、CMPUの制限を回避する可能性があります。

このことから、SMPUの重要な機能の1つは、アクセスを試みた発信元のバスマスターによるメモリアクセスをブロックできることに加え、他のマスターがそのメモリにアクセスすることもブロックできる点にあります。

まとめると:マイクロコントローラアーキテクチャにおいて、コアMPU(CMPU)は各コアからのメモリアクセスを監視し規制する上で重要な役割を果たします。CMPUはメモリ領域とその権限を適用し、違反が発生した場合に例外を発生させます。この機能は、スタックバッファオーバーフローのような一般的な攻撃ベクトルが任意のコード実行につながるのを防ぐなど、セキュリティ上極めて重要です。

一方、CMPUはコアに基づくメモリアクセスには対処できますが、DMAのような特殊な周辺機器を悪用した攻撃には対応できません。このギャップを埋めるのがシステムメモリ保護ユニット(SMPU)です。SMPUは各バスマスターごとにメモリアクセスを同時に監視・評価し、メモリ権限に対するきめ細かな制御を可能にします。本質的に、SMPUの発信元のマスターによるアクセスを規制する独自の能力は、周辺ハードウェアを利用した潜在的な攻撃を阻止し、全体的なシステムセキュリティを強化します。

SMPUの設定

前の段落では、CMPUとSMPUを適切に設定する重要性について説明しました。CMPUはコアで動作するアプリケーションコードがセキュリティや安全性の理由で禁止されたメモリ領域に直接アクセスするのを防ぎ、SMPUは間接的なメモリアクセスを防ぐ役割を果たします。

私たちが使用していたSPC58Nチップには、16のバスマスターごとに読み取り/書き込みアクセス制御権限を設定できる24のリージョンレジスタが搭載されていました。

各SMPUリージョンは、32ビットの開始アドレスと終了アドレス、および保護されたアドレス領域とリージョンフォーマットレジスタで構成されています。これにより、16のバスマスターごとに許可されるアクセス権限(読み取り、読み取り/書き込み、またはアクセス禁止)が定義されます。

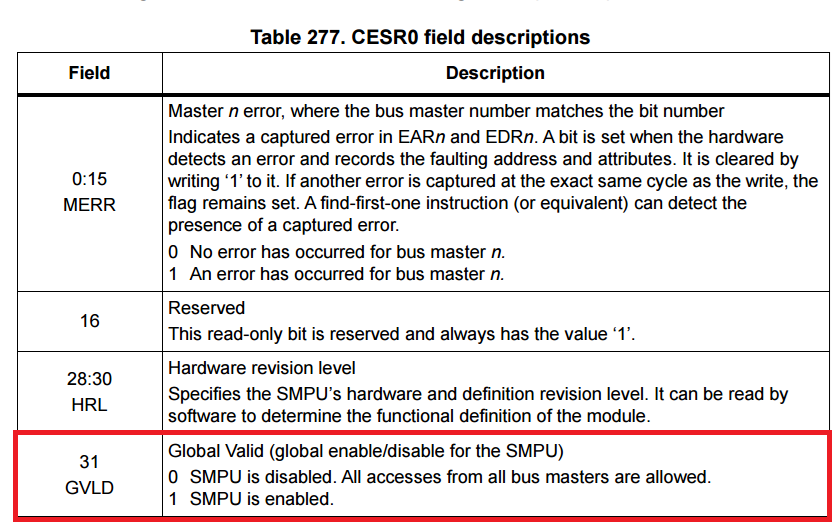

各リージョンには、それぞれ有効ビット(Valid Bit)と読み取り専用ビット(Read Only Bit)が設定されています。しかし、次のセクションで読み取り専用ビットについて詳しく説明する前に、もう1つ重要なSMPUレジスタであるCESR0レジスタについて触れておきましょう。

すべてが適切に設定されたら、制御/エラーステータスレジスタ0(CESR0)のGlobal Valid(GVLD)ビットを設定する必要があります。これにより、SMPUが有効化され、潜在的な攻撃に対抗する準備が整います。以下のように設定されます

リージョン読み取り専用ビット

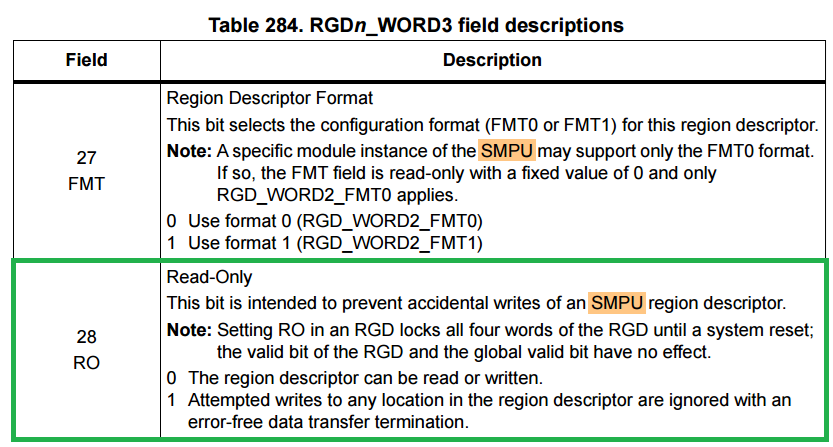

では読み取り専用ビットに話を戻しましょう。データシートを確認します。

読み取り専用(RO)ビットは、リージョンディスクリプタの意図しない変更を防ぐ役割を果たします。ROビットが設定されると、リージョンレジスタ内の任意の場所への書き込みが無視されます。これは非常に理にかなっており重要です。一度設定されたリージョンが、偶発的または悪意のある書き込みから保護されることが望ましいからです。しかし、ROビットの説明には以下のような注意書きもあります。

Source: RM0452 SPC58H, p. 536

上記の注意書きには、ROビットが設定されると、リージョン全体がロックされ、システムリセットまで変更できなくなると記載されています。この間、リージョンの有効ビット(Valid Bit)およびグローバル有効ビット(GVLD)には影響がなく、これらもシステムリセットまで変更することができません。

これは非常にスマートな防御策です。一度SMPUのリージョン情報が設定され、ROビットが有効化されると、グローバル有効ビット(GVLD)を操作することができなくなり、攻撃者がSMPUを無効化することができなくなります。SMPUを無効化する唯一の方法は次回のシステムリセット後となるため、攻撃者はデバイスへの支配を失うことになります。

SMPUの脆弱性

SMPUの設定を終えた後、システム全体のテストを開始しました。この製品では、1つのコアが安全性(ASIL-D)のアプリケーションを実行し、もう1つのコアがサードパーティのアプリケーションを実行するように構成されていました。当然ながら、2つのコアはメモリを共有していました。

SMPUは、安全性アプリケーションのメモリ領域(フラッシュ、EEPROM、SRAM)をアプリケーションコアからの読み取りおよび書き込みから保護するように設定されました。さらに、すべてのROビットが設定されていたため、システムリセットが行われるまでSMPUの保護を変更することはできないようになっていました。

ペネトレーションテスト中に、アプリケーションコア上で攻撃者をシミュレーションしました。

SPC58のデータシートには、ROビットを設定した後はGVLDビットがSMPUに影響を与えないと明記されていたにもかかわらず、このハードウェアメカニズムがシリコンには実装されていないことが判明しました。そのため、アプリケーションコア上の攻撃者がGVLDビットに0を書き込むことでSMPUを無効化し、セーフティコアのメモリに対して読み取りおよび書き込み操作を行うことが可能になりました。

たとえCMPUが正しく構成されていたとしても、SMPUが無効化されると、DMAやEthernetといったシステム周辺機器を通じて主要なメモリが攻撃にさらされる結果となっていました。

STMicroelectronicsへの開示

SPC58チップでこの挙動を確認した直後、私たちはSTMicroelectronicsのPSIRT(製品セキュリティインシデント対応チーム)に、この脆弱性に関するすべての関連情報を提供しました。

数回のやり取りの後、STMicroelectronicsからこの問題に関するエラッタ(訂正情報)を公開するとの回答があり、以下がその問題に対する回答の全文です。

「検出されたSMPUの挙動の逸脱は、非セキュアデバイスドメインに影響を及ぼす可能性があります。ただし、このドメインはセキュリティ情報を保存するために使用されるべきではありません。

秘密情報やセキュリティクリティカルなデータは、HSMサブシステムのメモリ内に保存する必要があります。それが外部に保存される場合は、暗号化が必要です。

SMPUはセキュリティ保護メカニズムではありません。例えば、SMPUは干渉を防ぐための補助機能として設計されています。」

STMicroelectronicsへの責任ある開示の時系列

| 2023年7月13日 | 潜在的なセキュリティ脆弱性に関する報告をSTに提出 |

| 2023年8月7日 | STMicroelectronicsから「エラッタは公開されるが、セキュリティ脆弱性ではない」との返信 |

| 2023年8月15日 | さらなる説明を記載した2通目のメールをSTに送信 |

| 2023年9月21日 | STからの返答「SMPUはセキュリティ保護メカニズムではありません」 |

| 2023年11月6日 | CVEリクエスト |

| 2023年11月20日 | CVE-2023-48010が割り当てられる |

影響のあるSTMicroelectronicsのパーツ9

- SPC58デバイス全て

- SR5E1

- SPC574K (K2)

- SPC572L (Lavaredo)

- SPC574Sx (Sphaero)

(2) CVE-2024-33882

そこで、NXPのMPC5748を選択しました。このチップは「自動車および産業用で制御およびゲートウェイ向けの非常に高い信頼性を持つMCU」10と説明されています。このNXP PowerPCがSTMicroelectronicsのPowerPCチップよりも優れたセキュリティ体制を持っているかどうかを確認する目的です。

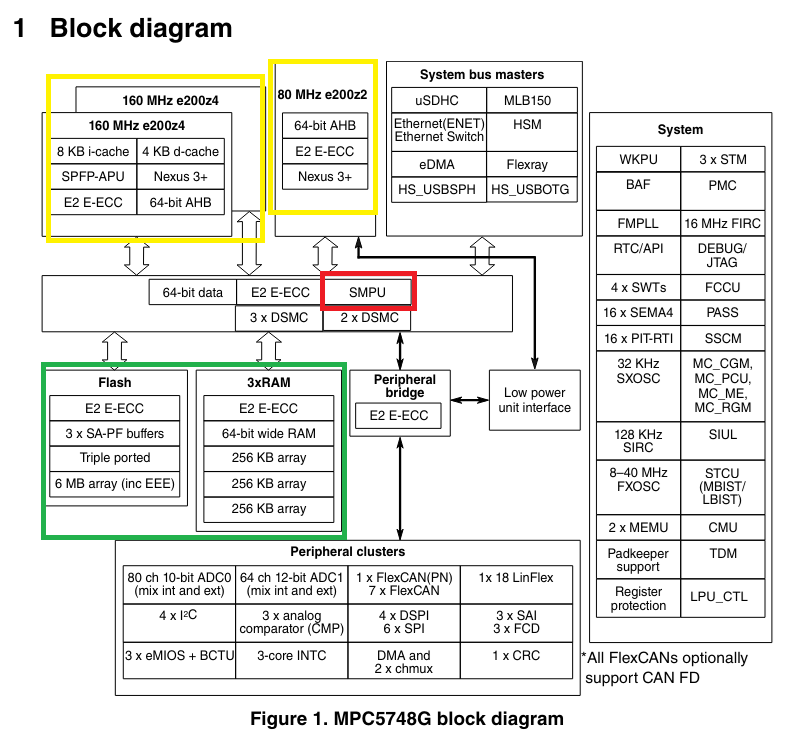

以下は、NXP MPC5748 PowerPCマイクロコントローラのブロック図11です。

上記のブロック図を見ただけで、疑問を抱かずにはいられませんでした。コアメモリ保護ユニット(CMPU)はどこにあるのでしょうか?

黄色で示した部分は3つのMCUコアを表していますが、どれもCMPUによって保護されていないようです。このシステムオンチップ(SoC)には、赤で示したシステムメモリ保護ユニット(SMPU)しか存在しないようです。緑で示した部分はチップのメモリです。

さらに調査を進めたところ、MPC5748のSMPUはCMPUの機能も兼ね備えていることが判明しました。これはつまり、STのSPC58で見つかったのと同じ脆弱性がMPC5748にも存在する場合、攻撃者はコア保護とシステム保護を含むメモリ保護システム全体を完全に無効化できることを意味します!

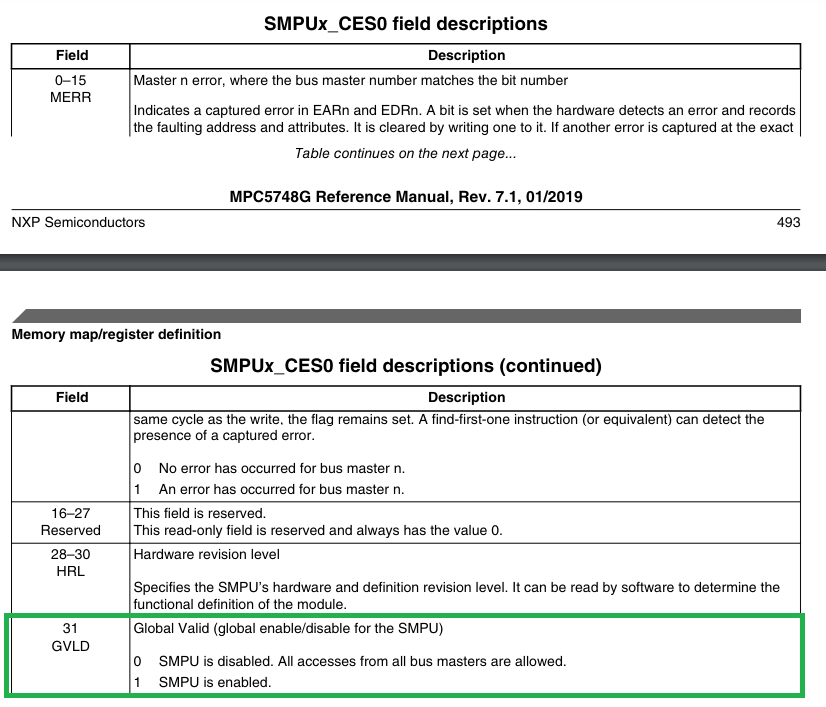

NXPのレジスタ名は、STMicroelectronicsのチップと非常に似ています。「Global Valid」GVLDビットは、SMPUx_CES0レジスタのビット31に位置しています。

出典:MPC5748Gリファレンスマニュアル, Rev. 7.1, p. 493-494

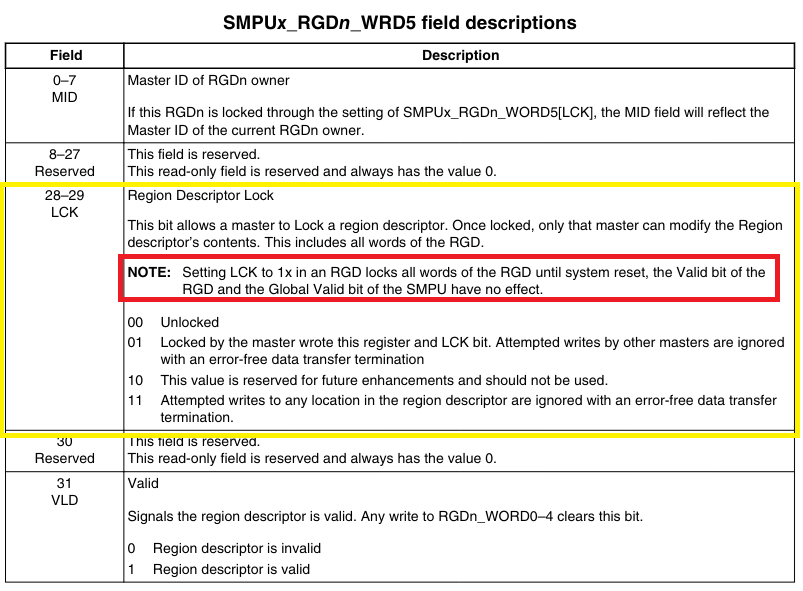

メモリ領域は、レジスタSMPUx_RGDn_WRD5で定義されています

Source: MPC5748G Reference Manual, Rev. 7.1, p. 505

STMicroelectronicsのSPC58と非常によく似ており、リージョン・ディスクリプタ・ロック(LCK)またはSPC58での読み取り専用ビット(RO)は、メモリ保護領域を設定後にロックするために使用されます(上記の黄色で示されています)。赤い部分の注意書きもSPC58のものと似ているようです。

ここでもSPC58マイクロコントローラの場合と同様に、記述はほぼ同一です。リージョンをロックすると、SMPUのグローバル有効ビット(Global Valid)が無効になり、SMPUを無効化できなくなるとされています。

しかし、簡単なテストで判明したのは、SMPUが有効化され、すべてのLCKビットがロックされている状態でも、特権を持つ攻撃者がGlobal Validを0に設定することで、SMPUを完全に無効化できるということです。別にCMPUが存在しないため、SMPUを無効化することで攻撃者はメモリ空間全体に対して制限なしの読み取り/書き込み/実行アクセスを得ることができます。

NXPへの開示

MPC5748チップでこの挙動を確認した直後、私たちはNXPのPSIRT(製品セキュリティインシデント対応チーム)に、この脆弱性に関するすべての関連情報を提供しました。

何度かのやり取りの後、NXPはドキュメントの記述が不明確であることを認め、この夏(具体的な日付は未定)に誤解を防ぐためのドキュメントのエラッタを公開すると述べました。しかし、NXPはSMPUがセキュリティ機能ではないと明言しました。

以下にNXPの回答全文を示します12。

「本製品のリファレンスマニュアルは、SMPUがセキュリティ機能ではないことを明確に記載しています。SMPUは『セキュリティ概要』の章や『セキュリティモジュール』のセクションではなく、『システムモジュール』のセクションに記載されています。また、SMPUは『機能一覧』表の『セキュリティ』の項目には含まれておらず、SMPUを説明する章でも『セキュリティ』という用語は使用されていません。」

しかし、MPC5748チップのリファレンスマニュアルを読み進めても、SMPUがセキュリティ機能ではないという明確な記述は見つかりませんでした。それどころか、リファレンスマニュアルの第21章第2節のSMPUに関するパラグラフには、次のように記載されています。

「システムメモリ保護ユニット(SMPU)は、システムバスメモリ参照のためのハードウェアアクセス制御を提供します。SMPUは、システムバストランザクションを同時に監視し、メモリ空間とそのアクセス権を定義する事前プログラム済みのリージョン・ディスクリプタを使用して、それらの適切性を評価します。十分なアクセス制御権限を持つメモリ参照は処理が許可されますが、どのリージョン・ディスクリプタにもマッピングされていない、または権限が不十分な参照は、アクセスエラー応答となります」13

リファレンスマニュアルでは、SMPUについて直接的または間接的にも言及していません。ただし、SMPUについて書かれた章では、SMPUがMCUのメモリ空間へのアクセス権限を制御する役割を担っていると記載されています。これはコンピュータセキュリティの基本とも言える概念です。

NXPへの責任ある開示の時系列

| 2024年2月28日 | NXPに最初のメール通知 |

| 2024年2月28日 | NXPが内部IDを割り当て |

| 2024年3月21日 | NXPへリマインダーメールを送信 |

| 2024年3月21日 | NXPの回答 – 調査を進行中 |

| 2024年3月28日 | NXPから返信 ‐ 注意書きの表現が曖昧であると認め、エラッタが公開される予定。挙動は仕様通りとのこと。 |

| 2024年3月31日 | NXPへさらなる説明を含むメール送信、 SMPUはセキュリティメカニズムであり、これが実装上の脆弱性であると説明。 |

| 2024年4月4日 | NXPからの最終回答 – NXPはこれをセキュリティ問題としては認識しないとの見解。 |

| 2024年4月16日 | CVEリクエスト |

| 2024年4月28日 | CVE-2024-33882が割り当てられる |

軽減策

- 重要なセキュリティメカニズム、例えばMPUなどに関するデータシートの記載を信頼する前に、自身でテストを行うか、外部のペネトレーションテストベンダーを利用するなどして、必ずその主張を検証してください。

- また、MCUのエラッタ(訂正情報)を必ず確認してください。これには、チップのセキュリティ状況に関する重要な情報が含まれている場合があります。

- CVE-2023-48010に関連して: ハードウェアのメカニズムをセキュリティ目的で信頼できない場合(上述のSMPUの例のように)、そのメカニズムに依存しないでください!同等のセキュリティレベルを達成するための他の方法を探すか、安全で確実な方法で利用できるようにしてください。たとえば、STMicroelectronics MCUにあるCMPUのような他のメモリ保護ユニットを利用することを検討してください。

結論

本論文を通じて示してきたように、メモリ保護ユニット(MPU)はすべてのマイクロコントローラの防御戦略において重要な役割を果たしています。MPUは、自動車アプリケーションのコンテクストにおいて不可欠であり、車両内のECUや組み込みシステムのセキュリティ、信頼性、安全性を向上させます。そのため、共有リソースに対するアクセス制御を実行するために設計されたハードウェアメカニズムがセキュリティ機能ではない、というNXPやSTMicroelectronicsの主張を受け入れるのは極めて困難なように思います。

両社とも、特定の操作手順に従えばSMPUを無効化できなくなると明確に述べていますが、私たちが示したように、グローバル有効ビット(Global Valid Bit)をロックするはずだったハードウェア部分が実装されておらず、その結果、特権を持つ攻撃者がSMPUを無効化し、通常アクセス不可能な機密メモリ領域にアクセスできることが判明しました。

- 出典: https://www.techtarget.com/searchsecurity/definition/access-control#:~:text=Access%20control%20is%20a%20security,access%20control%3A%20physical%20and%20logical. ↩︎

- W. Stallings, L. Brown, Computer Security: Principles and Practice, 3rd Edition, p. 114 ↩︎

- Nicolas Dejon, Chrystel Gaber, Gilles Grimaud. From MMU to MPU: adaptation of the Pip kernel to constrained devices. 3rd International Conference on Internet of Things & Embedded Systems (IoTE 2022), Dec 2022, Sydney, Australia. ffhal-03705114v2f ↩︎

- https://hal.science/hal-03705114v2/file/FromMMUToMPUAdaptationOfThePipKernelToConstrainedDevices-IoTE2022-Final.pdf p. 2 ↩︎

- バストランザクションとは、コンピュータ化されたシステム内で、バスによって接続された2つのデバイス間でデータや制御情報を交換することを指します。バスは、コンピュータシステム内の複数のデバイスが互いに通信できるようにする通信経路です。 ↩︎

- https://en.wikipedia.org/wiki/PowerPC_e200 ↩︎

- ASIL D(Automotive Safety Integrity Level D)は、ISO 26262規格内で定義されている初期ハザード(傷害リスク)の最も高い分類を指します。このレベルは、合理的ではない残余リスクを回避するために適用される最も厳格な安全対策の水準を示しています。 ↩︎

- これは、STMicroelectronicsがPowerPCマイクロコントローララインに付けた商標名です。 ↩︎

- この影響を受けるMCUのリストは、2024年3月13日にSTMicroelectronicsからメールで送信されました。 ↩︎

- https://www.nxp.com/products/processors-and-microcontrollers/power-architecture/mpc5xxx-microcontrollers/ultra-reliable-mpc57xx-mcus:MPC57XX ↩︎

- https://www.nxp.com/docs/en/data-sheet/MPC5748G.pdf, p. 4 ↩︎

- この返信は、2024年4月4日に送信されたメールからのものです。 ↩︎

- MPC5748G Reference Manual, Rev. 7.1, 01/2019, p. 479 ↩︎

執筆:2024年12月03日